- Is logicworks 5 a vhdl how to#

- Is logicworks 5 a vhdl full#

- Is logicworks 5 a vhdl verification#

- Is logicworks 5 a vhdl code#

Only thing that will change is well write different VHDL Code and will try out more test cases. Well try some more circuits, but the basic procedure will remain same. Make sure you remember the different LogicWorks tools and controls you just learnt. Take some time to look back and familiarize with the procedure of Coding and Testing You should change the values of input ports only and observe theĪt this point you have successfully wrote and tested the VHDL code for a two input AND gate I/OPanelDefault.html file from the Script Code not Editable While Simulation is running Same as VHDL->Run SimulationStop Simulation Users can define systems and components Features a subset of the industry-standard VHDL language and fully mixes high-level language and structural design methods.

Generated VHDL stub corresponding to a Digital Circuit black-box For that there is LogicWorks 4.5 available directly from Capilano Computing (.) which supports MacOS 9 and X but doesnt include VHDL support.

Is logicworks 5 a vhdl verification#

Specific, not as versatileĮasy to design Large Scale and complex circuits through modular approach of programming.Įasy verification of your design without having to use expensive hardware.įaster and more robust design with the codetestimprove cycle. LogicWorks software was originally developed on and for the Macintosh OS but version 5.0 doesnt support the Macintosh. (1)Start LogicWorks Start the LogicWorks program by double-clicking on the LW5 icon. You’ll also be presented with a standard save dialogue box. LogicWorks used the pins that you specied in Step 3 to construct the entity declaration. Once stored properly, they could be used like any other devices in the Library. For a VHDL model, you’ll be presented with a VHDL skeleton (an entity declaration and the shell of an architecture body). Vhdl Testbench Example Code Bing - This vhdl testbench example. To start the process, select 'New Source' from the menu items under 'Project'. Drawing: Fixed: Problem created in Model Wizard in 5.0. VHDL Testbench Vhdl Testbench Example Code Bing - From the above code, the Xilinx ISE environment makes is simple to build the basic framework for the testbench code.

Is logicworks 5 a vhdl how to#

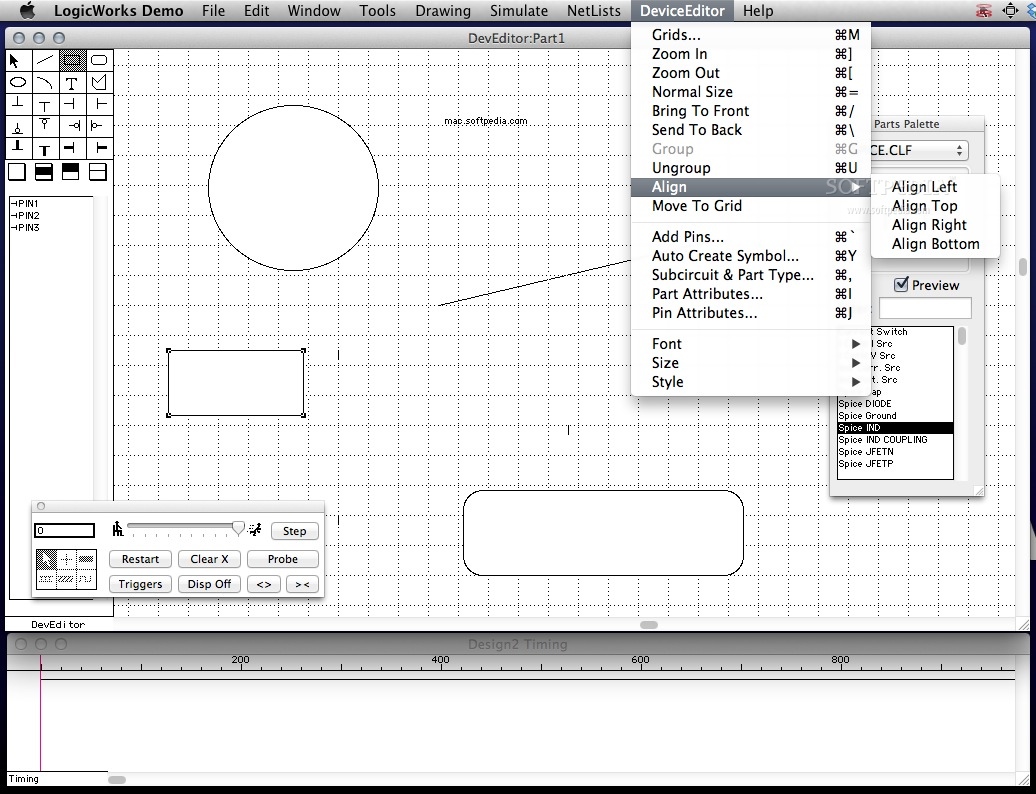

In this Lab experiments, we are going to learn how to create our own device symbols. LogicWorks 5 for Windows - Version History. View Notes - Tutorial1 from CMPT 250 at Simon Fraser University.

Used to model only digital circuit system. Creating our own devices in LogicWorks 5. Sometimes Inputs are given in parallel(e.g. Changes made to signal connections or device parameters on the screen are immediately reflected in the timing waveforms and probes placed right on the diagram.A high level language to describe digital circuitĭifferent that a programming language ( such as Java) : This is coupled with the unique, interactive digital simulator. VHDL has become the industry standard method for describing digital systems in a high-level language, and an understanding of it is now essential for any working circuit designer.

Is logicworks 5 a vhdl full#

LogicWorks includes a full schematic editor with bussing, multi-level Undo/Redo, interactive connection tracing, and many other powerful features. The major change in LogicWorks 5 from previous versions is the addition of VHDL simulation. LogicWorks is so easy to use that students will be creating and testing circuits in a matter of minutes, instead of spending precious lab time just getting started. Build a circuit using majority4 and the other I/O devices in LogicWorks 5 to verify the truth table of. What is the best way to implement a digital clock in VHDL June 4th, 2019 - From Clock Generation here it is a clock with a period of T 4 ns code architecture declarative part signal clock std ulogic 1 architecture statement part clock lt not clock after 2 ns code In a real implementation of a VHDL simulation VHDL How should I create a clock in. This means that you can study advanced concepts much more quickly and clearly using on-screen simulation than you can by spending time wiring up expensive and damage-prone parts in a lab. Create a VHDL Model for a Device Symbol majority4. The package gives you the power, speed and flexibility to create and test an unlimited number of circuit elements on-screen. No other software tool makes digital design easier, faster or more interactive than LogicWorks. LogicWorks is an interactive circuit design tool intended for teaching and learning digital logic.

0 kommentar(er)

0 kommentar(er)